Features

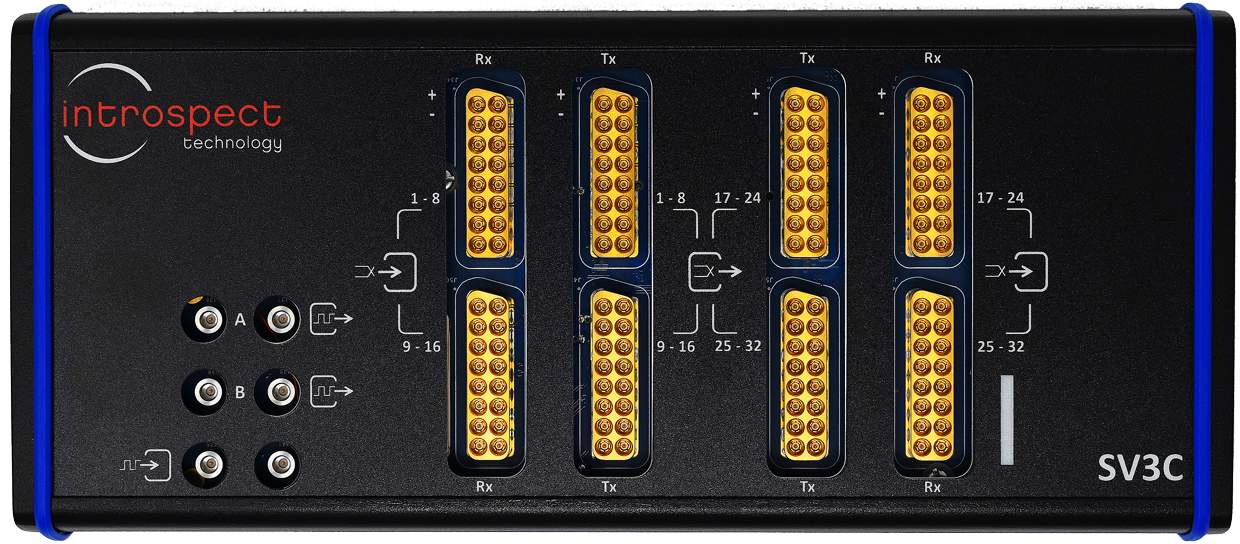

- Highest level of integration at 32 lanes in a handheld form factor

- Fully synthesized integrated jitter injection on all lanes

- Flexible pre-emphasis, equalization, and clock recovery per lane

- Flexible loopback support per lane

- Single-ended or differential low-speed I/O for digital test vector processing

- Reconfigurable, protocol customization (on request)

- State of the art programming environment – Our Award Winning Pinetree™ development environment

- Integrated device control through SPI, I2C, or JTAG

Applications

- Parallel PHY validation of serial bus standards

- Interface test of electrical/optical media such as Backplanes, Cables, Pluggables: CFP, SFP, SFP+

- Plug-and-play system-level validation

- Timing verification: • PLL transfer function measurement • Clock recovery bandwidth verification • Frequency ppm offset characterization

- Mixed-technology applications: • High-speed ADC and DAC (JESD204) data capture and/or synthesis • FPGA-based system development • Channel and device emulation

- Clock-recovery triggering for external oscilloscope or BERT equipment