- The SPI core in the SV6E-X can act as a controller that can perform read and write transactions on any SPI target

- The SPI device can also act as a target, and it contains built-in emulation modes for typical flash memories

- Supports single data rate (SDR) mode as well as double data rate (DDR) mode

- Precision timing generator capable of adjusting data to clock setup time with a resolution of 100 ps

- SV6E-X can receive the SCLK and then inject fine-resolution delays on read-back data that is clocked by this SCLK

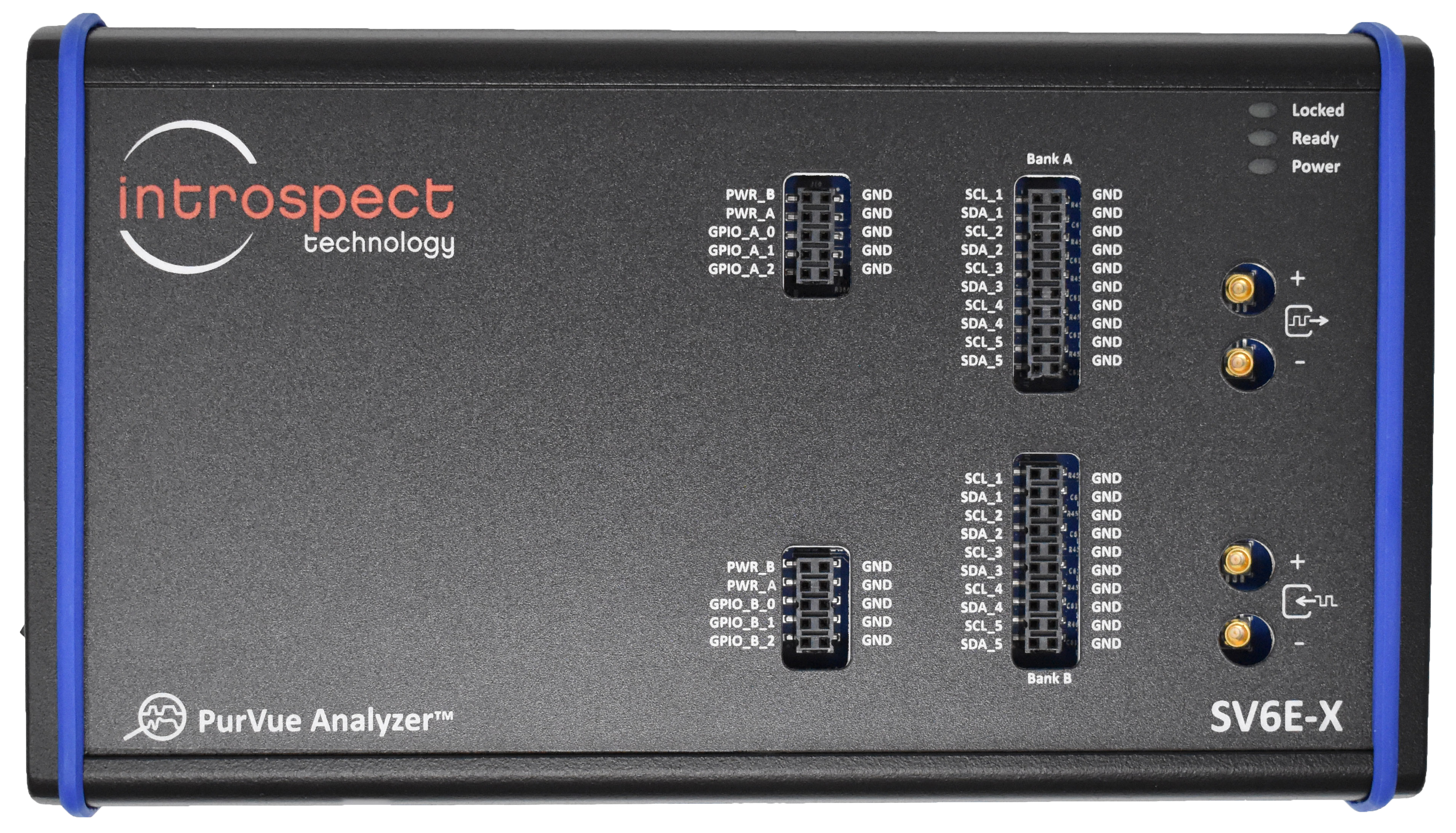

- Optional PurVue Analyzer™ technology available on any I/O channel (two-channel, 1 Gsps, 500 MHz real-time oscilloscope)

- Please refer to the Pinetree API for a detailed listing of all methods and all attributes of these device classes.

| Name | SV6E-SPI |

|---|---|

| Description | SV6E-X preconfigured with SPI License |

| Protocols Supported | SPI, Quad SPI and Octal SPI |