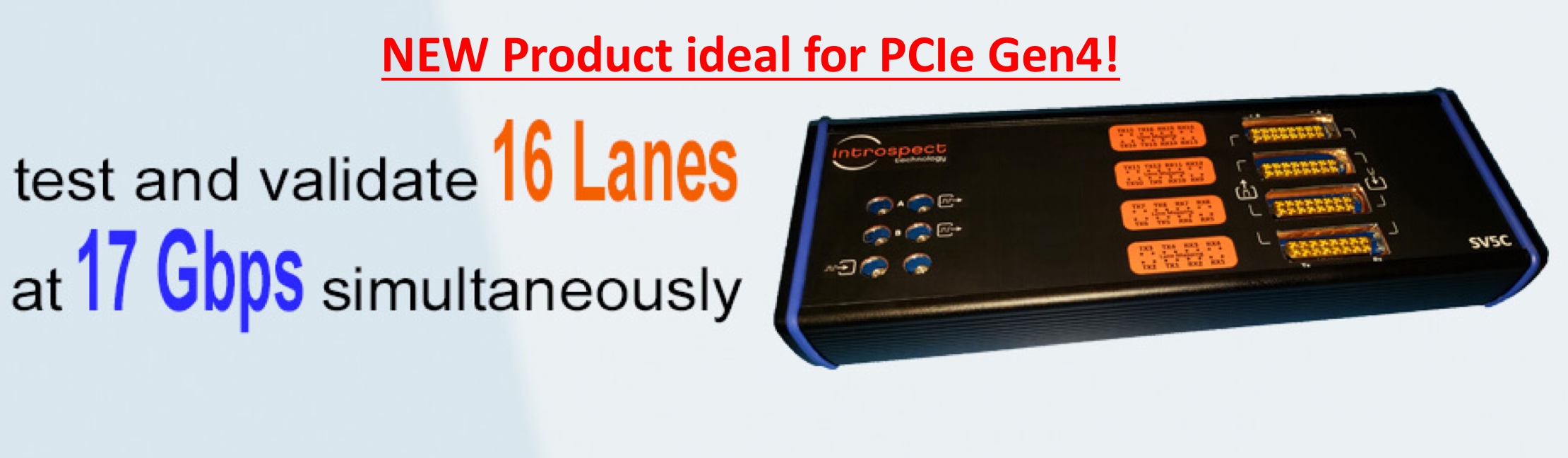

SV5C Series

SV5C Series

The SV5C Personalized SerDes Tester is a highly capable, highly integrated parallel BERT solution that allows for achieving enhanced test coverage and gaining deep insights into multi-channel interface link performance. By simultaneously generating and measuring traffic on 16 lanes and at data rates up to 17 Gbps, the SV5C offers a unique opportunity to characterize SerDes links under realistic system-like conditions while offering world class signal integrity and isolation between channels.

Designed from the ground up to address the validation needs of parallel interfaces such as PCI Express Gen 4 and various upcoming MIPI standards, the SV5C is a technological marvel incorporating innovations in the areas of digital signal processing, analog processing, microwave signal propagation, data analytics, thermal design, and many others!

When used with the Introspect ESP Software, the SV5C becomes an integral part of a complete high-volume characterization station that consists of a test automation suite, device power supplies, device handlers, and device control probes.

Highlights:

- Fully-synthesized integrated jitter injection on 16 lanes

- Fully-automated integrated jitter testing on 16 lanes

- Optimized pattern generator rise-time for receiver stress test applications

- Fully synthesized voltage noise injection on 16 lanes

- Full suite of driver programmability (differential, common-mode, equalization)

- Clock recovery and receiver equalization per lane

- State of the art programming environment based on the highly intuitive Python language

- Integrated device control through SPI, I2C, or JTAG

- Reconfigurable, protocol customization (on request)

| Model | Description | Max Data Rate | Tx Channels | Rx Channels | Configuration |

|---|