### DATA SHEET

# SV5C-DPTXCPTX

## MIPI D-PHY / C-PHY Generator

## **C** SERIES

© Introspect Technology, 2023 Published in Canada on November 16, 2023 EN-D017E-E-23320

INTROSPECT.CA

#### TABLE OF CONTENTS

## Table of Contents

| Introduction                    | 3 |

|---------------------------------|---|

| Overview                        | 3 |

| Key Benefits                    | 3 |

| Applications                    | 3 |

| Physical Connections            | 4 |

| MXP High Speed Connector Pinout | 4 |

| Low Speed GPIO Connector Pinout | 5 |

| Ordering Information            | 5 |

| Specifications                  | 6 |

|                                 |   |

## Introduction

#### **OVERVIEW**

The SV5C-DPTXCPTX MIPI D-PHY/C-PHY Generator is an ultra-portable, high-performance instrument that enables characterization and validation of MIPI D-PHY and C-PHY receiver ports. The instrument operates over a continuous range of data rates and includes analog parameter controls that enable deep insights into receiver voltage sensitivity, receiver skew and jitter tolerance for receiver stress-testing.

The instrument operates with the easy-to-use, highly versatile Pinetree software environment for automated physical layer compliance testing. Pinetree also includes pattern synthesis tools that enable the generation of complete DSI-2 or CSI-2 packets such as color bars and active image frames for system-level test.

This document describes the electrical characteristics and key specifications of the D-PHY and C-PHY Generator. Please refer to User Manual documentation for operating instructions.

#### **KEY BENEFITS**

- Any-rate operation to 9.0 Gbps per lane (D-PHY) and 6.5 Gsps per trio (C-PHY)

- Per-lane HS voltage level and common-mode control

- Per-lane LP voltage level control

- Per-lane skew injection with < 1 ps resolution

- Per-lane multi-source jitter injection

- State-of-the-art programming environment based on the highly intuitive Python language

#### **APPLICATIONS**

- Parallel physical layer validation

- DSI and CSI packet and protocol testing

- Plug-and-play system-level validation

INTRODUCTION

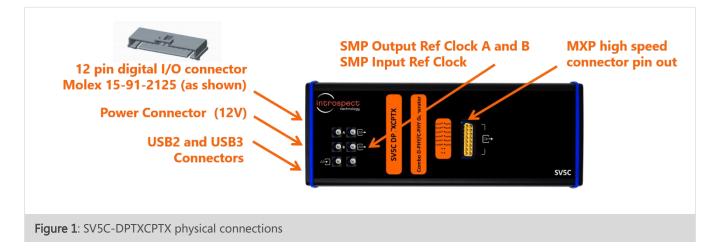

#### **PHYSICAL CONNECTIONS**

#### MXP HIGH SPEED CONNECTOR PINOUT

#### MXP PIN **D-PHY PINOUT C-PHY PINOUT** Trio 1 A Lane 1 P 1 MXP 2 Lane 1 N Trio 1 B Top View 3 Lane 2 P Trio 1 C 4 Lane 2 N Trio 3 A 5 Lane 3 P Trio 3 B 9 1 Lane 3N Trio 3 C 6 2 $\cap$ 10 7 NC NC 3 11 NC 8 NC 12 4 ( ) ()9 Lane 4 P Trio 2 A 5 $\cap \cap$ 13 10 Lane 4 N Trio 2 B 6 14 $\bigcirc$ ()NC 11 Trio 2 C 12 NC Trio 4 A 7 $\bigcirc \bigcirc$ 15 13 CLK P Trio 4 B 8 16 14 CLK N Trio 4 C 15 NC NC 16 NC NC

#### TABLE 1: SIGNAL MAPPING OF THE MXP CONNECTOR FOR SV5C-DPTXCPTX

#### LOW SPEED GPIO CONNECTOR PINOUT

#### TABLE 2: GPIO CONNECTOR PINOUT

| CONNECTOR                               | PIN | FUNCTION                          |

|-----------------------------------------|-----|-----------------------------------|

|                                         | 1   | User IO 0                         |

|                                         | 2   | User IO 1                         |

|                                         | 3   | Reserved                          |

| 12-pin GPIO connector                   | 4   | Reserved                          |

| Molex 15-91-2125                        | 5   | Reserved                          |

|                                         | 6   | User IO 2                         |

| 000000000000000000000000000000000000000 | 7   | User IO 3                         |

|                                         | 8   | SV5C reset pin, active low        |

| T T                                     |     | ("0" = reset, "1" = not in reset) |

| Pin 12 Pin 1                            |     | Minimum pulse width = 50 ns       |

| All User IO pins use                    | 9   | I2C SCL Controller                |

| 1.8V LVCMOS logic and have a            |     | Software controlled               |

| weak internal pull-up.                  | 10  | I2C SDA Controller                |

| (specifications in Table 11).           |     | Software controlled               |

|                                         | 11  | Tearing effect input              |

|                                         |     | Rising edge triggered             |

|                                         | 12  | Ground                            |

#### **ORDERING INFORMATION**

#### TABLE 3: ITEM NUMBERS FOR THE SV5C-DPTXCPTX AND RELATED PRODUCTS

| PART NUMBER | NAME                | KEY DIFFERENTIATORS                    |

|-------------|---------------------|----------------------------------------|

| 5786        | SV5C-DPTXCPTX       | Supports both D-PHY and C-PHY          |

| 5782        | SV5C-DPTX           | D-PHY only                             |

| 5783        | SV5C-CPRX           | C-PHY only                             |

| 5793        | SV5C TX PHY Upgrade | License to add the C-PHY functionality |

## Specifications

#### TABLE 4: GENERAL SPECIFICATIONS

| PARAMETER                                      | VALUE              | UNITS | DESCRIPTION AND CONDITIONS                                                                                                         |

|------------------------------------------------|--------------------|-------|------------------------------------------------------------------------------------------------------------------------------------|

| Application / Protocol Support                 |                    |       |                                                                                                                                    |

| Physical layer interface                       | D-PHY<br>C-PHY     |       |                                                                                                                                    |

| MIPI protocol                                  | CSI/DSI            |       | Flexible pattern architecture allows for<br>the generation of encoded PHY data,<br>unencoded PHY data, or entire CSI/DSI<br>frames |

| LP/HS Handling                                 | Automatic          |       | Automatically generates LP and HS data                                                                                             |

| Ports                                          |                    |       |                                                                                                                                    |

| Number of D-PHY Lanes                          | 4 Lanes<br>and CLK |       | Supports embedded clock for MIPI<br>D-PHY v3.5                                                                                     |

| Number of C-PHY Trios                          | 4 Trios            |       |                                                                                                                                    |

| Number of Dedicated Output<br>Reference Clocks | 2                  |       | Individually synthesized frequency and output format                                                                               |

| Number of Dedicated Input<br>Reference Clocks  | 1                  |       | Used as external reference clock input                                                                                             |

| Number of Trigger Inputs                       | 2                  |       | Via Molex connector                                                                                                                |

| Number of Flag Outputs                         | 2                  |       | Via Molex connector                                                                                                                |

| Number of I2C/I3C Masters                      | 1                  |       | Via Molex connector                                                                                                                |

| Connections to PC for accessing<br>Pinetree    | 2                  |       | USB2 and USB3                                                                                                                      |

| Power Consumption                              |                    |       |                                                                                                                                    |

| DC Input Voltage                               | 12                 | Volt  |                                                                                                                                    |

| Current Draw                                   | 8.0                | Amp   | 9.0 Gbps / 4 Lane D-PHY operation                                                                                                  |

| Current Draw                                   | 8.0                | Amp   | 6.5 Gsps / 4 Trio C-PHY operation<br>PRBS9 pattern, HS amplitude = 200 mV                                                          |

#### TABLE 5: DATA RATES AND REFERENCE CLOCKS

| PARAMETER                           | VALUE | UNITS | DESCRIPTION AND<br>CONDITIONS   |

|-------------------------------------|-------|-------|---------------------------------|

| Data Rates and Frequencies          |       |       |                                 |

| Minimum Dragrammakla Data Data      | 100   | Mbps  | D-PHY                           |

| Minimum Programmable Data Rate      | 80    | Msps  | C-PHY                           |

| Mavimum Programmable Data Data      | 9.0   | Gbps  | D-PHY                           |

| Maximum Programmable Data Rate      | 6.5   | Gsps  | C-PHY                           |

| Frequency Resolution of Programmed  | 1     | kHz   |                                 |

| Data Rate                           |       |       |                                 |

| Minimum External Input Clock        | 10    | MHz   |                                 |

| Frequency                           |       |       |                                 |

| Maximum External Input Clock        | 250   | MHz   |                                 |

| Frequency                           |       |       |                                 |

| Supported External Input Clock I/O  |       |       | LVDS (typical 400 mVpp input)   |

| Standards                           |       |       | LVPECL (typical 800 mVpp input) |

| Minimum Output Clock Frequency      | 10    | MHz   |                                 |

| Maximum Output Clock Frequency      | 250   | MHz   |                                 |

| Output Clock Frequency Resolution   | 1     | kHz   |                                 |

| Supported External Output Clock I/O |       |       | LVDS, LVPECL, CML, HCSL, and    |

| Standards                           |       |       | LVCMOS                          |

#### TABLE 6: HS VOLTAGE CHARACTERISTICS

| PARAMETER                        | VALUE           | UNITS    | DESCRIPTION AND<br>CONDITIONS |

|----------------------------------|-----------------|----------|-------------------------------|

| Output Coupling                  |                 |          |                               |

| Output Differential Impedance    | 100             | Ohm      |                               |

| Differential Impedance Tolerance | +/- 10          | Ohm      |                               |

| Output Single-Ended Impedance    | 50              | Ohm      |                               |

| Single-Ended Impedance Tolerance | +/- 5           | Ohm      |                               |

| HS Voltage Performance           |                 |          |                               |

| Minimum Output Voltage           | 20              | mV       | D-PHY, differential           |

| Amplitude                        | 20              | mV       | C-PHY, single ended           |

| Maximum Output Voltage           | 600             | mV       | D-PHY, differential           |

| Amplitude                        | 400             | mV       | C-PHY, single ended           |

| Voltage Swing Resolution         | 20              | mV       | D-PHY, differential           |

|                                  | 20              | mV       | C-PHY, single ended           |

| Voltage Swing Accuracy           | >5% or<br>10 mV | %, mV    |                               |

|                                  | -100            | mV       | D-PHY                         |

| Minimum Common Mode Voltage      | -400            | mV       | C-PHY                         |

| Mayimum Common Made Valtage      | 500             |          | D-PHY                         |

| Maximum Common Mode Voltage      | 1000            | mV       | C-PHY                         |

| Common Mode Voltage Resolution   | 1               | mV       | D-PHY or C-PHY                |

| Common Made Voltage Accuracy     | >5% or          | %, mV    |                               |

| Common Mode Voltage Accuracy     | 10 mV           | 70, IIIV |                               |

| Rise and Fall Time               | 50              | ps       | Typical, 20% to 80%           |

| Swing and Common Mode Setting    | Per Lane        |          | D-PHY                         |

| swing and common mode setting    | Per Trio        |          | C-PHY                         |

#### TABLE 7: LP VOLTAGE CHARACTERISTICS

| PARAMETER                                   | VALUE          | UNITS | DESCRIPTION AND<br>CONDITIONS                                      |

|---------------------------------------------|----------------|-------|--------------------------------------------------------------------|

| LP Voltage Controls                         |                |       |                                                                    |

| Minimum Programmable LP Logic<br>High Level | 0              | mV    | LP voltage control specifications apply<br>to both D-PHY and C-PHY |

| Maximum Programmable LP Logic<br>High Level | 1300           | mV    |                                                                    |

| Minimum Programmable LP Logic<br>Low Level  | -100           | mV    |                                                                    |

| Maximum Programmable LP Logic<br>Low Level  | 600            | mV    |                                                                    |

| Logic Level Control Resolution              | 1              | mV    |                                                                    |

| Logic Level Accuracy                        | >2% or<br>5 mV | %, mV |                                                                    |

#### TABLE 8: HS JITTER AND NOISE CHARACTERISTICS

| PARAMETER                          | VALUE   | UNITS  | DESCRIPTION AND<br>CONDITIONS |

|------------------------------------|---------|--------|-------------------------------|

| Jitter and Noise Performance       |         |        |                               |

| Random Jitter (RMS)                | < 1.3   | ps rms | D-PHY, differential           |

|                                    |         |        | C-PHY, single ended           |

| Random Jitter (RMS)                | < 1.7   | ps rms | 1.0 Gsps, HS-only 444 pattern |

|                                    | < 1.3   | ps rms | 6.5 Gsps, HS-only 444 pattern |

| Minimum Frequency of Injected      | 0.1     | kHz    | D-PHY or C-PHY                |

| Deterministic Jitter               |         |        |                               |

| Maximum Frequency of Injected      | 50      | MHz    | D-PHY or C-PHY                |

| Deterministic Jitter               |         |        |                               |

| Frequency Resolution of Injected   | 0.1     | kHz    | D-PHY or C-PHY                |

| Deterministic Jitter               |         |        |                               |

| Maximum Peak to Peak               | 2       | UI     | D-PHY or C-PHY , numerically  |

| Deterministic Jitter               |         |        | generated, tested to 1000 ps  |

| Magnitude Resolution of Injected   | 500     | fs     | D-PHY or C-PHY                |

| Deterministic Jitter               |         |        |                               |

| Accuracy of Injected Deterministic | >10% or | %, ps  | D-PHY or C-PHY                |

| Jitter                             | 10 ps   |        |                               |

| Common Mode Noise Injection        | 1       | MHz    |                               |

| Minimum Sinusoidal Frequency       |         |        |                               |

| Common Mode Noise Injection        | 1       | GHz    |                               |

| Maximum Sinusoidal Frequency       |         |        |                               |

| Common Mode Noise Injection        | 1000    | mV     | Measured single ended         |

| Maximum Sinusoidal Amplitude       |         |        |                               |

#### TABLE 9: HS CHANNEL SKEW CHARACTERISTICS

| PARAMETER                      | VALUE | UNITS | DESCRIPTION AND<br>CONDITIONS          |

|--------------------------------|-------|-------|----------------------------------------|

| Channel Skew Performance       |       |       |                                        |

| Coarse Skew Range:             |       |       |                                        |

| Minimum Programmable Skew,     | -20   | UI    | D-PHY, Lane to Lane                    |

| in Integer UI                  | -20   | UI    | C-PHY, Trio to Trio                    |

| Coarse Skew Range:             |       |       |                                        |

| Maximum Programmable Skew,     | +20   | UI    | D-PHY, Lane to Lane                    |

| in Integer UI                  | +20   | UI    | C-PHY, Trio to Trio                    |

| Coarse Skew Resolution         |       |       |                                        |

| 1.0 Gbps / 1.0 Gsps            | 0.125 | UI    | D-PHY, Lane to Lane                    |

| 9.0 Gbps / 6.5 Gsps            | 1.0   | UI    | C-PHY, Trio to Trio                    |

| Fine Skew Range:               |       |       |                                        |

| Minimum Programmable Skew      | -500  | ps    | D-PHY, HS Clock to Data                |

|                                | -500  | ps    | C-PHY, Wire to Wire                    |

|                                |       |       | Testing limit – hardware is capable of |

|                                |       |       | larger skews                           |

| Fine Skew Range:               |       |       |                                        |

| Maximum Programmable Skew      | +500  | ps    | D-PHY, HS Clock to Data                |

|                                | +500  | ps    | C-PHY, Wire to Wire                    |

|                                |       |       | Testing limit – hardware is capable of |

|                                |       |       | larger skews                           |

| Fine Skew Injection Resolution | 1     | ps    | D-PHY or C-PHY                         |

#### TABLE 10: HS PATTERN HANDLING CHARACTERISTICS

| PARAMETER                                          | VALUE | UNITS  | DESCRIPTION AND<br>CONDITIONS                                                                                |

|----------------------------------------------------|-------|--------|--------------------------------------------------------------------------------------------------------------|

| User-Programmable Pattern Memory                   |       |        |                                                                                                              |

| Minimum Pattern Segment Size                       | 8     | Bits   |                                                                                                              |

| Maximum Pattern Segment Size                       | 8     | GBytes |                                                                                                              |

| Total Memory Space for Transmitters                | 8     | GBytes |                                                                                                              |

| Pattern Sequencer                                  |       |        |                                                                                                              |

| Sequence Control                                   | Yes   |        | Loop infinite<br>Loop-on-count (see count below)<br>Play to end                                              |

| Number of Sequencer Slots per<br>Pattern Generator | 16    |        | Each pattern generator can string up<br>to 16 different segments together,<br>each with its own repeat count |

| Number of Entry Slots                              | 1     |        | Separate from above 16 segments                                                                              |

| Number of Exit Slots                               | 1     |        | Separate from above 16 segments                                                                              |

| Maximum Repeat Count Per Slot                      | 65536 |        |                                                                                                              |

| Maximum Repeat Count for Outer<br>Loop             | 65536 |        | Outer loop can encompass any number of slots                                                                 |

| Additional Pattern Characteristics                 |       |        |                                                                                                              |

| Escape Mode Command Entry                          | Yes   |        | Per Lane                                                                                                     |

| Pattern Switching                                  | Yes   |        | Wait to end of segment, or immediate                                                                         |

#### TABLE 11: GPIO AND 12C VOLTAGE CHARACTERISTICS

| PARAMETER               | VALUE | UNITS | DESCRIPTION AND<br>CONDITIONS     |

|-------------------------|-------|-------|-----------------------------------|

| Voltage                 |       |       |                                   |

| Voltage Level           | 1.8   | V     | All GPIOs operate at 1.8 V LVCMOS |

| V <sub>IL</sub> minimum | -0.3  | V     |                                   |

| V <sub>IL</sub> maximum | 0.6   | V     |                                   |

| V <sub>IH</sub> minimum | 1.2   | V     |                                   |

| V <sub>IH</sub> maximum | 2.1   | V     |                                   |

| V <sub>OL</sub> maximum | 0.45  | V     |                                   |

| V <sub>OH</sub> minimum | 1.35  | V     |                                   |

| REVISION NUMBER | HISTORY                                                                                           | DATE              |

|-----------------|---------------------------------------------------------------------------------------------------|-------------------|

| 1.0             | Document release                                                                                  | July 27, 2020     |

| 1.1             | Fixed error in the data rate specification                                                        | July 27, 2020     |

| 1.2             | Updated D-PHY data rate specification                                                             | July 14, 2021     |

| 1.3             | Updated specifications and added<br>description of GPIO pinout and<br>GPIO voltage specifications | April 11, 2022    |

| 1.4             | Replaced Introspect ESP Software for Pinetree                                                     | July 26, 2023     |

| 1.5             | Added embedded clock in table 4                                                                   | November 16, 2023 |

The information in this document is subject to change without notice and should not be construed as a commitment by Introspect Technology. While reasonable precautions have been taken, Introspect Technology assumes no responsibility for any errors that may appear in this document.

© Introspect Technology, 2023 Published in Canada on November 16, 2023 EN-D017E-E-23320

INTROSPECT.CA