**DATA SHEET**

# SV5C-CPRX

MIPI C-PHY Analyzer

# **C SERIES**

# **Table of Contents**

| Introduction                                        | 3  |

|-----------------------------------------------------|----|

|                                                     |    |

| Overview                                            | 3  |

| Key Benefits                                        | 3  |

| Physical Connections                                | 4  |

| MXP High Speed Connector Pinout                     | 4  |

| Ordering Information                                | 5  |

| Feature Description                                 | 5  |

|                                                     |    |

| Complete C-PHY Receiver Implementation              | 6  |

| Hardware CRC Checking and Packet Error Rate Testing | 7  |

| Protocol Analysis                                   | 7  |

| Protocol Analysis: Advanced Trigger Modes           | 9  |

| Protocol Analysis: Acquisition Duration             | 11 |

| Specifications                                      |    |

# Introduction

#### **OVERVIEW**

The SV5C-CPRX MIPI C-PHY Analyzer is an ultra-portable, high-performance instrument that enables characterization and validation of MIPI C-PHY transmitter ports. The analyzer operates at up to 6.5 Gsps and combines analog signal measurement capabilities with sophisticated capture and compare modes for complete C-PHY packet analysis. The instrument operates using the highly versatile Introspect ESP Software environment, including a full suite of tools for DSI-2 and CSI-2 video frame extraction. The software enables test automation for packet error rate testing, protocol timing analysis and MIPI CTS.

#### **KEY FEATURES**

- **C-PHY Physical Layer**: four C-PHY trio receivers with integrated LP/HS signaling and support for a continuous range of symbol rates up to 6.5 Gsps

- C-PHY Protocol Layer: fully supports CSI-2 and DSI-2 pixel formats, DSI-2 DSC and V-DCM decompression, and DSI Display Command Sets (DCS)

- Physical Layer Analysis: analog waveform capture for HS and LP, complete C-PHY decoding (HS wire, wirestate, symbol, and data), precision time stamps for physical layer events

- **Protocol Layer Analysis**: packet error rate testing, full video frame extraction and analysis, and sophisticated capture modes triggered on physical layer and protocol layer events

#### **KEY BENEFITS**

- **Self-Contained**: an all-in-one system enables the simplest bench environment for physical layer test to full protocol layer validation

- Automated: leverages the full power of Python and the award-winning Introspect ESP Software. Scripting capability is ideal for debug tasks and for full-fledged production screening of devices and systems

- Future Proof: protect your investment by adopting a high-performance tool for multiple product applications and across a large span of data rates

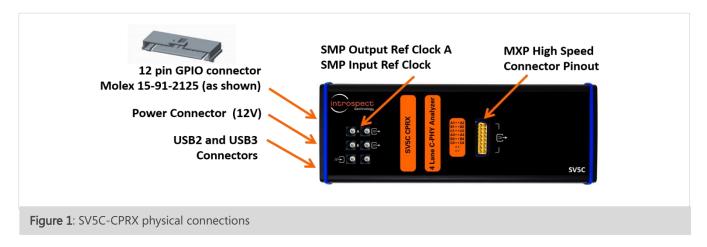

## PHYSICAL CONNECTIONS

## MXP HIGH SPEED CONNECTOR PINOUT

TABLE 1: SIGNAL MAPPING OF THE MXP CONNECTOR FOR SV5C-CPRX

|          | MXP PIN | C-PHY PINOUT |

|----------|---------|--------------|

|          | 1       | Trio 1 A     |

| MXP      | 2       | Trio 1 B     |

| Top View | 3       | Trio 1 C     |

|          | 4       | Trio 3 A     |

| 1 0 0 9  | 5       | Trio 3 B     |

| 2 0 0 10 | 6       | Trio 3 C     |

| 3 0 11   | 7       | NC           |

|          | 8       | NC           |

| 4 0 0 12 | 9       | Trio 2 A     |

| 5 0 13   | 10      | Trio 2 B     |

| 6 0 14   | 11      | Trio 2 C     |

| 7 0 15   | 12      | Trio 4 A     |

| 8 0 16   | 13      | Trio 4 B     |

|          | 14      | Trio 4 C     |

|          | 15      | NC           |

|          | 16      | NC           |

#### ORDERING INFORMATION

#### TABLE 2: ITEM NUMBERS FOR THE SV5C-CPRX AND RELATED PRODUCTS

| PART<br>NUMBER | NAME                                 | KEY DIFFERENTIATORS                        |  |

|----------------|--------------------------------------|--------------------------------------------|--|

| 5785           | 1                                    | C-PHY physical and protocol layer analyzer |  |

| 3763           | (includes Introspect ESP SW license) | for links up to 6.5 Gsps                   |  |

| 5786           | SV5C-DPTXCPTX MIPI Generator         | D-PHY / C-PHY Generator for links up to    |  |

| 3700           | (includes Introspect ESP SW license) | 9.0 Gbps (D-PHY) and 6.5 Gsps (C-PHY)      |  |

# **Feature Description**

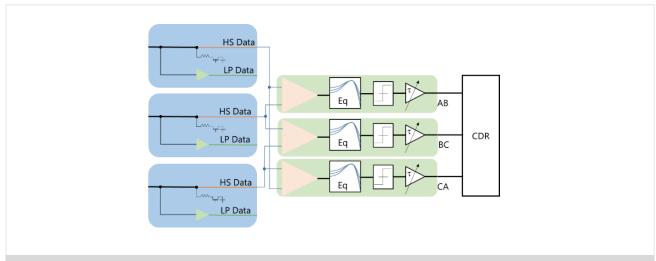

### **COMPLETE C-PHY RECEIVER IMPLEMENTATION**

The SV5C-CPRX MIPI C-PHY Analyzer is a complete, integrated, 4-trio C-PHY receiver providing the analog front-end circuitry for C-PHY as well as a complete protocol back-end. As shown in Figure 2, each lane contains low power (LP) programmable threshold voltage detectors, dynamically controlled C-PHY termination resistors and fully differential high-speed (HS) receivers with 3-wire C-PHY clock and data recovery. The real-time behavior of the CPRX enables broad acquisition capabilities for physical-layer and protocol-layer testing. The analyzer also supports ALP-Mode operation.

Figure 2: SV5C-CPRX receiver detail illustrating LP detection, automatic termination switches, and high-speed receivers

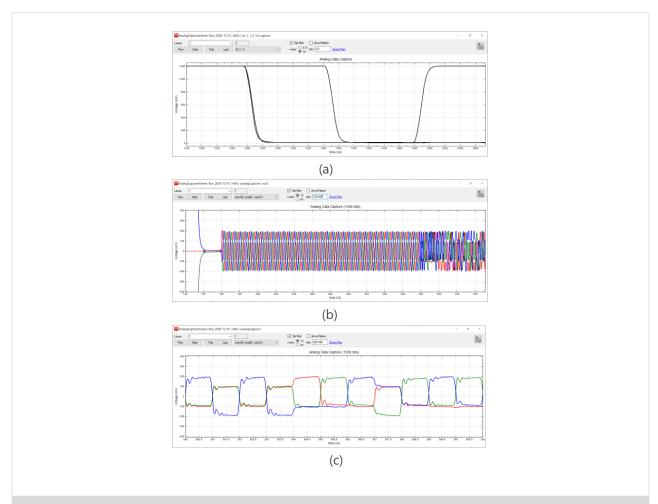

#### ANALOG SIGNAL CAPTURE

The SV5C-CPRX provides analog waveform capture capability for both single ended LP and differential HS signals as shown in Figure 3 below. Periodic HS signals can be sampled at a resolution of 128 points per UI for symbol rates up to 6.5 Gsps. HS measurements including rise and fall time, and strong and weak amplitude levels are automatically extracted. Periodic single-ended LP signals are sampled at a resolution of 2.5 ns. LP measurements including rise time and amplitude are automatically extracted. High speed waveform acquisitions are triggered on packet starts, or may be triggered continuously, while LP signals may be triggered on a number of conditions including LP pulse width. The HS and LP analog capture tools enable deep-dive signal integrity investigations for physical layer debug and enable conformance testing such as the MIPI CTS.

**Figure 3:** SV5C-CPRX analog waveform capture capability in Introspect ESP software: (a) LP analog capture from a ULPS waveform (b) HS analog capture, T3-preamble (c) HS analog capture, close-up of wire AB, wire BC, and wire CA

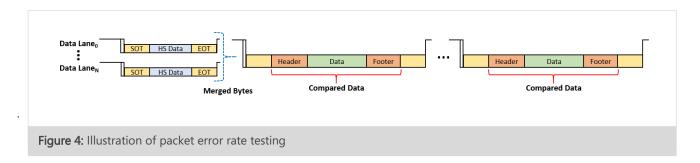

#### HARDWARE CRC CHECKING AND PACKET ERROR RATE TESTING

A fundamental feature of the SV5C-CPRX MIPI C-PHY Analyzer is hardware-based packet error-rate test (PERT) capability. Similar to the traditional BER test, the PERT enables the measurements of real C-PHY transmissions from CSI or DSI generators. As illustrated in Figure 4, the Analyzer detects and filters all signal waveforms and compares only the packet data transmitted between SOT and EOT, registering errors after the data has been merged between lanes, thereby comparing errors in packets rather than bits.

#### **PROTOCOL ANALYSIS**

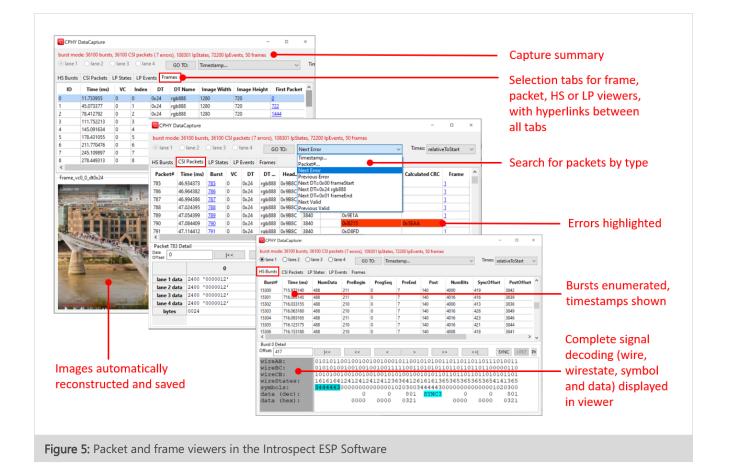

The SV5C-CPRX MIPI C-PHY Analyzer is a complete protocol analyzer for both camera and display serial interfaces. The analyzer adjusts its viewer displays based on the protocol being measured. Figure 5 on the following page shows analysis features available in the Introspect ESP Software, including viewers for:

- **HS Bursts:** view each high-speed burst, by lane, with quick statistics of the time of arrival in nanoseconds, SYNC offset and captured wire states, symbols, and data integers in each

- CSI/DSI Packets: merged traffic from all lanes may be viewed as unique packets, headers are

decoded for easy, high-level viewing, and errors (header CRC, payload CRC, ECC) are

automatically highlighted

- LP States: each LP state is captured along with its time of arrival and duration; this viewer is extremely effective for building a visualization of the physical layer events

- Frames: images are automatically reconstructed and saved, even if incomplete, with details such as pixel format, virtual channel, and image dimensions shown in the viewer.

#### PROTOCOL ANALYSIS: ADVANCED TRIGGER MODES

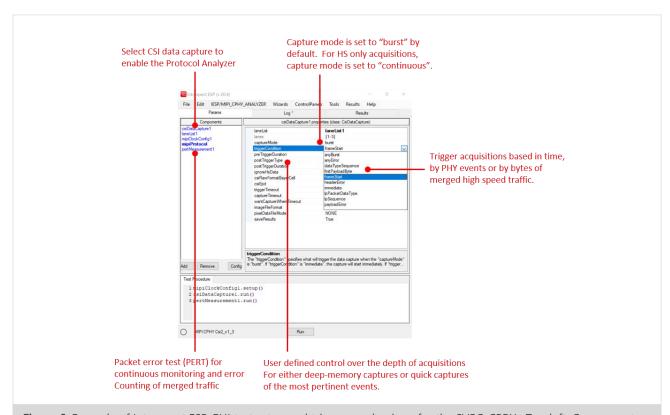

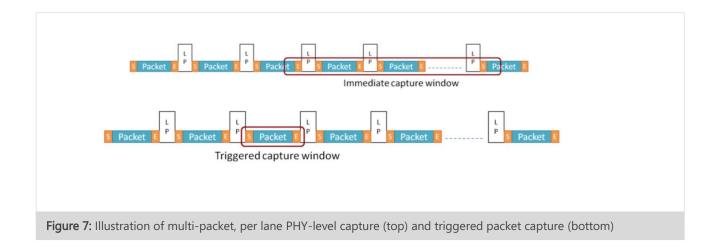

Figure 6 shows the Introspect ESP Software user interface for defining the trigger mechanisms within the analyzer. At the highest level, the analyzer can be programmed to perform immediate captures (in which all data is measured irrespective of LP transitions) or triggered captures. Each is as illustrated in Figure 7.

In triggered capture modes, the C-PHY analyzer automatically handles LP and HS received signals and resistor termination. The analyzer waits for a valid LP to HS entry sequence before enabling a capture, and when a valid HS-entry transition is detected, the capture starts immediately. If no valid HS-entry transition is detected, the capture returns an empty array.

Table 3 provides a list of trigger conditions that are available in the Analyzer. The duration of data captured before the trigger condition is specified in software by "preTriggerDuration" settings. The duration of data captured after the trigger condition is specified in software by "postTriggerDuration" settings. The specification of post trigger duration is described in the following section.

**Figure 6:** Example of Introspect ESP GUI test setup and trigger mechanisms for the SV5C-CPRX. Top left: Components window, showing selected CSI, DSI and PHY data acquisition methods. Top right: Properties window, showing CSI Data Capture. Bottom: Test Procedure window, with Python code calling components.

TABLE 3: TRIGGER CONDITIONS

| TRIGGER<br>CONDITION<br>NAME | TYPE OF<br>EVENT                                                   | TRIGGER DESCRIPTION                                                                           |  |

|------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|

| Immediate                    | Time-Based                                                         | time-based acquisition, beginning immediately                                                 |  |

| anyBurst                     | PHY                                                                | the first high-speed burst recorded on any data lane                                          |  |

| IpSequence                   | PHY                                                                | user-defined sequence of LP states, e.g. "111,001,000" reflects a proper LP-HS entry sequence |  |

| anyError                     | CSI, DSI                                                           | the first error is registered: header, CRC or payload                                         |  |

| dataTypeSequence             | CSI, DSI user-defined integer value to be identified in a packet h |                                                                                               |  |

| headerError                  | CSI, DSI                                                           | protocol layer, the first error recognized in a packet header                                 |  |

| payloadError                 | CSI, DSI                                                           | protocol layer, the first error recognized in a packet header                                 |  |

| firstPayloadByte             | CSI, DSI                                                           | user-defined byte to be identified in the payload                                             |  |

| IpPacketDataType             | CSI, DSI                                                           | user-defined integer value to identified in LP packet                                         |  |

| frameStart                   | CSI                                                                | CSI-only, any packet with header data type 0x00 indicating the                                |  |

| Trainestart CSI              |                                                                    | beginning of a frame                                                                          |  |

| verticalSyncStart            | DSI                                                                | DSI-only, any packet with header data type 0x01 indicating the beginning of a frame           |  |

### PROTOCOL ANALYSIS: ACQUISITION DURATION

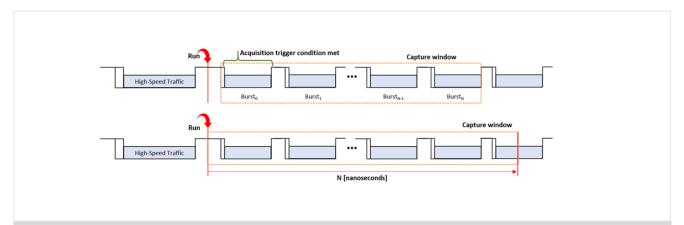

The acquisition duration is determined according to the "postTriggerType", and may be specified in terms of time, in terms of PHY events, or in terms of bytes of merged high-speed traffic. Figure 8 illustrates two methods of determining acquisition length in terms of PHY events. In Figure 8 (top), an acquisition begins on the first high-speed burst observed and completes after a user-defined number of bursts are recorded. In Figure 8 (bottom), an acquisition begins and the analyzer records for a user-defined period of N nanoseconds.

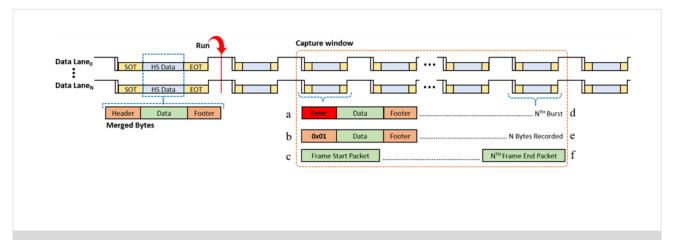

Figure 9 illustrates three examples of triggering acquisitions on merged, high-speed data. The acquisition start condition is user-defined as either: (a) an error within a packet header, (b) a variable data type identifier, here chosen as 0x01 and (c) a frame start packet (CSI only). The duration of the acquisition for each is chosen according to the number of N received: (d) bursts, (e) bytes and (f) frame end packets.

Table 4 provides a list of conditions for determining the acquisition duration.

**Figure 8:** Illustration of two event-based acquisitions. Above, acquisition is triggered on the first observed burst and the duration is determined by a user-defined number of N bursts. Below, acquisition begins immediately, and the duration is for a user-defined period of N nanoseconds

**Figure 9:** Illustration of three acquisitions triggered on merged high-speed traffic events: (a) a header error, (b) a user-defined data type identifier and (c) a frame start packet. Three conditions for specifying the acquisition duration are shown: (d) a user-defined number of N bursts, (e) a number of bytes, and (f) a number of frames

TABLE 4: SPECIFICATION OF ACQUISITION DURATION

| SPECIFICATION OF ACQUISITION DURATION | TYPE OF<br>EVENT | TRIGGER DESCRIPTION                                                  |

|---------------------------------------|------------------|----------------------------------------------------------------------|

| durationInNs                          | Time-Based       | time-based acquisition, defined in nanoseconds                       |

| numberOfBursts                        | PHY              | the total number of unique bursts acquired, across all data lanes    |

| numberOfBytes                         | PHY              | the total number of bytes recorded between SOT and EOT of all bursts |

| numberOfLpCommands                    | PHY              | the number of LP commands acquired                                   |

| numberOfLpStates                      | PHY              | The number of unique LP states, e.g. "111,001,000" would be 3        |

| numberOfFrameEnds                     | CSI              | protocol layer, the number of frame-end packets recorded             |

| numberOfVerticalSyncStarts            | DSI              | protocol layer, the number of packets with data type identifier 0x01 |

# Specifications

# TABLE 5: GENERAL SPECIFICATIONS

| PARAMETER                        | VALUE     | UNITS | DESCRIPTION AND CONDITIONS             |

|----------------------------------|-----------|-------|----------------------------------------|

| Application / Protocol           |           |       |                                        |

| Physical Layer Interface         | C-PHY     |       |                                        |

| MIPI Protocol                    | CSI, DSI  |       | CSI-2 v1.3, v2.0, v3.0, DSI-2 v1.1     |

| LS/HS Handling                   | Automatic |       |                                        |

| ALP Mode                         | Yes       |       |                                        |

| Ports                            |           |       |                                        |

| Number of C-PHY Trios            | 4 Trios   |       |                                        |

| Number of Dedicated Output       | 2         |       | Individually synthesized frequency and |

| Reference Clocks                 |           |       | output format                          |

| Number of Dedicated Input        | 1         |       | Used as external reference clock input |

| Reference Clocks                 |           |       | Osed as external reference clock input |

| Number of Trigger Inputs         | 2         |       | Via Molex connector                    |

| Number of Flag Outputs           | 2         |       | Via Molex connector                    |

| Number of I2C/I3C Masters        | 1         |       | Two pins: SCL and SDA                  |

| Nulliber of 12C/13C Masters      | 1         |       | via Molex connector                    |

| Connections to PC for Introspect | 2         |       | USB2 (module control)                  |

| ESP Software Control             |           |       | USB3 (data transfer)                   |

| Power Consumption                |           |       |                                        |

| DC Input Voltage                 | 12        | V     |                                        |

| Maximum Current Draw             | TBD       | Α     |                                        |

# TABLE 6: C-PHY SYMBOL RATES AND REFERENCE CLOCKS

| PARAMETER                                 | VALUE | UNITS | DESCRIPTION AND CONDITIONS      |

|-------------------------------------------|-------|-------|---------------------------------|

| Symbol Rates / Frame Rates                |       |       |                                 |

| Minimum HS Symbol Rate                    | 80    | Msps  | Each Trio                       |

| Maximum HS Symbol Rate                    | 6.5   | Gsps  | Each Trio                       |

| Frequency Resolution of HS Symbol<br>Rate | 1     | ksps  |                                 |

| Minimum LP Toggle Rate                    | 0     | MHz   |                                 |

| Maximum LP Toggle Rate                    | 20    | MHz   |                                 |

| Reference Clock Frequencies               |       |       |                                 |

| Minimum External Input Clock              | 10    | MHz   |                                 |

| Frequency                                 |       |       |                                 |

| Maximum External Input Clock              | 250   | MHz   |                                 |

| Frequency                                 |       |       |                                 |

| Supported External Input Clock I/O        |       |       | LVDS (typical 400 mVpp input)   |

| Standards                                 |       |       | LVPECL (typical 800 mVpp input) |

| Minimum Output Clock Frequency            | 10    | MHz   |                                 |

| Maximum Output Clock Frequency            | 500   | MHz   |                                 |

| Output Clock Frequency Resolution         | 1     | kHz   |                                 |

| Supported External Output Clock           |       |       | LVDS, LVPECL, CML, HCSL, and    |

| I/O Standards                             |       |       | LVCMOS                          |

TABLE 7: C-PHY RECEIVER CHARACTERISTICS

| PARAMETER                         | VALUE     | UNITS   | DESCRIPTION AND CONDITIONS     |

|-----------------------------------|-----------|---------|--------------------------------|

| Input Coupling                    |           |         |                                |

| Input Impedance                   | 50        | ohm     | HS transmission, each wire     |

| Input Impedance                   | Hi-Z      |         | LP transmission                |

| HS / LP Voltage                   |           |         |                                |

| Minimum  V <sub>ID</sub>   Weak   | 90        | mV      | Measured at SV5C MXP connector |

| Maximum  V <sub>ID</sub>   Strong | 300       | mV      | Measured at SV5C MXP connector |

| Minimum Programmable LP           | -100      | mV      |                                |

| Threshold                         | -100      | IIIV    |                                |

| Maximum Programmable LP           | 1300      | mV      |                                |

| Threshold                         | 1300      | 111 V   |                                |

| Timing Generator Performance      |           |         |                                |

| Timing Resolution                 | 7.8125    | mUl     | Measured at 6.5 Gsps           |

| Differential Non-Linearity Error  | +/- 0.5   | LSB     |                                |

| Integral Non-Linearity Error      | +/- 5     | ps      |                                |

| Range                             | Unlimited |         |                                |

| Global Timing Performance         |           |         |                                |

| Minimum T <sub>LPX</sub>          | 50        | ns      |                                |

| Minimum T <sub>3-PREPARE</sub>    | 38        | ns      |                                |

| Minimum T <sub>3-PREBGIN</sub>    | 28        | symbols |                                |

| Minimum T <sub>3-POST</sub>       | 7         | symbols |                                |

# TABLE 8: PATTERN HANDLING CHARACTERISTICS

| PARAMETER                     | VALUE | UNITS | DESCRIPTION AND CONDITIONS             |

|-------------------------------|-------|-------|----------------------------------------|

| Features                      |       |       |                                        |

|                               | RAW,  |       | RAW6, RAW7, RAW8, RAW10, RAW12,        |

| Supported Pixel Formats (CSI) | RGB,  |       | RAW14, RAW16, RAW20, RGB444, RGB555,   |

|                               | YUV   |       | RGB565, RGB666, RGB888, YUV420, YUV422 |

|                               |       |       | RGB101010, RGB121212, RGB332, RGB565,  |

| Currented Divel Formats (DCI) | RGB   |       | RGB666, RGB888, YCbCr420_12bit,        |

| Supported Pixel Formats (DSI) | YCbCr |       | YCbCr422_16bit, YCbCr422_20bit,        |

|                               |       |       | YCbCr422_24bit                         |

| Decompression Support (DSI)   | Yes   |       | DSC, V-DCM                             |

| Display Command Set (DSI)     | Vas   |       |                                        |

| Support                       | Yes   |       |                                        |

| Memory Depth                  | 8     | GByte | For received packet data               |

TABLE 9: PACKET AND FRAME ANALYSIS

| PARAMETER                                  | VALUE | UNITS | DESCRIPTION AND CONDITIONS                                                    |

|--------------------------------------------|-------|-------|-------------------------------------------------------------------------------|

| Features                                   |       |       |                                                                               |

| HS Data Rate Detection                     | Yes   |       | Automatic                                                                     |

| CSI / DSI Packet Analysis                  | Yes   |       | Header, Payload, ECC extraction, data type detection, virtual channel support |

| Frame Analysis                             | Yes   |       | Image width / height detection Pixel format and frame rate detection          |

| CRC and ECC Analysis                       | Yes   |       | Payload error and header error detection, Packet error statistics             |

| Trigger Conditions for Data<br>Capture     | Yes   |       | Refer to Table                                                                |

| Specification of Data Acquisition Duration | Yes   |       | Refer to Table                                                                |

## TABLE 10: TRIGGER, FLAG, AND I2C BUS VOLTAGE CHARACTERISTICS

| PARAMETER               | VALUE | UNITS | DESCRIPTION AND CONDITIONS        |

|-------------------------|-------|-------|-----------------------------------|

| Voltage                 |       |       |                                   |

| Voltage Level           | 1.8   | V     | All GPIOs operate at 1.8 V LVCMOS |

| V <sub>IL</sub> minimum | -0.3  | V     |                                   |

| V <sub>IL</sub> maximum | 0.6   | V     |                                   |

| V <sub>IH</sub> minimum | 1.2   | V     |                                   |

| V <sub>IH</sub> maximum | 2.1   | V     |                                   |

| V <sub>OL</sub> maximum | 0.45  | V     |                                   |

| V <sub>OH</sub> minimum | 1.35  | V     |                                   |

| Revision Number | History               | Date             |

|-----------------|-----------------------|------------------|

| 1.0             | Document Release      | January 15, 2021 |

| 1.1             | Product Number Update | August 25, 2021  |

The information in this document is subject to change without notice and should not be construed as a commitment by Introspect Technology. While reasonable precautions have been taken, Introspect Technology assumes no responsibility for any errors that may appear in this document.