## DATA SHEET

# MIPI D-PHY Generator

## **C SERIES**

© Introspect Technology, 2024 Published in Canada on September 19, 2024 MK-D013E-E-24263

INTROSPECT.CA

TABLE OF CONTENTS

## Table of Contents

| Introduction                                             | 3  |

|----------------------------------------------------------|----|

| Overview                                                 | 3  |

| Key Features                                             | 3  |

| Key Benefits                                             | 3  |

| Ordering Information                                     | 4  |

| Key Features                                             | 4  |

| Physical Description and Pinout                          | 4  |

| Physical Description and Pinout<br>Data Rate Performance | 7  |

| Integrated LP and HS Generation                          | 7  |

| HS Timing Controls                                       | 8  |

| Complete Physical Layer Testing                          | 8  |

| Protocol Layer Testing                                   | 10 |

| Pinetree Software Interface                              | 10 |

| MIPI Compliance Test Suites (CTS)                        | 12 |

| Input and Output Reference Clocks                        | 13 |

| General Purpose I/O (GPIO) and I2C Bus                   | 14 |

| Specifications                                           | 15 |

## Introduction

## **OVERVIEW**

The **SV3C-DPTX MIPI D-PHY Generator** is an ultra-portable, high-performance instrument that enables characterization and validation of MIPI D-PHY receiver ports. The instrument operates at up to 6.5 Gbps and includes analog parameter and precision timing controls that enable deep insights into receiver performance, including voltage and skew sensitivities and jitter tolerance.

The instrument operates with the easy-to-use, highly versatile Pinetree software environment which includes a full suite of tools for generation of packets, test patterns, color bars and video frames for both CSI-2 and DSI-2. Pinetree enables complete automation for MIPI D-PHY receiver testing and MIPI compliance test suites (CTS) are available.

## **KEY FEATURES**

- **D-PHY Physical Layer:** four D-PHY lanes with integrated LP/HS signaling and support for a continuous range of data rates from 80 Mbps to 6.5 Gbps

- **D-PHY Protocol Layer:** fully supports CSI-2 and DSI-2-pixel formats, DSI-2 DSC and V-DCM decompression, and DSI-2 Display Command Sets (DCS)

- Voltage Controls: HS amplitude, HS common mode voltage, and LP voltage levels

- **Timing Impairments:** per-lane skew injection with < 1 ps resolution and per-lane multi-source jitter injection

### **KEY BENEFITS**

- **Self-Contained**: an all-in-one system that enables the simplest bench environment for physical layer test to full protocol layer validation

- Automated: leverages the full power of Python and Introspect's award-winning software, Pinetree, with scripting capabilities ideal for debug tasks and for full-fledged production screening of devices and systems

- **Future Proof**: protect your investment by adopting a high-performance tool for multiple product applications and across a large span of data rates

#### **ORDERING INFORMATION**

TABLE 1: ITEM NUMBERS FOR THE SV3C-DPTXCPTX AND RELATED PRODUCTS

| PART NUMBER | ΝΑΜΕ                                                  | KEY DIFFERENTIATORS                                                  |

|-------------|-------------------------------------------------------|----------------------------------------------------------------------|

| 4584        | DPTX D-PHY Generator                                  | SV3C-DPTX with full impairment capability including jitter injection |

| 4591        | DPTX-APIX – Speed<br>Upgrade Option for D-PHY         | Speed upgrade option to 6.5 Gbps                                     |

| 4593        | DPTX Upgrade to include<br>C-PHY Generator Capability | Combination D-PHY and C-PHY generation capability                    |

| 4595        | CPTX-SPD1: Speed Upgrade<br>Option for C-PHY          | Speed upgrade option for C-PHY to 4.5 Gsps                           |

## **Product Features**

## PHYSICAL DESCRIPTION AND PINOUT

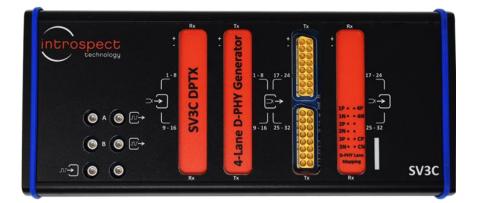

Figure 1 shows a diagram of the physical ports of the SV3C-DPTX.

The SV3C-DPTX has two high-speed MXP connectors. The lower MXP connector, as shown in Figure 1, provides the differential TX lanes 1-4 and the differential clock output signal. The pin mapping for the lower connector is provided in Table 2. No-connect (NC) pins should not be used.

The upper MXP connector shown in Figure 1 provides three replica signals which may be connected directly to an external measurement device for live monitoring. The pin mapping for the upper connector is provided in Table 3.

#### TABLE 2: LOWER MXP CONNECTOR, LANE PINOUT

| CONNECTOR                                                                                    | PIN                    | LANE             |

|----------------------------------------------------------------------------------------------|------------------------|------------------|

|                                                                                              | 1, 2                   | TX Lane 1 (P, N) |

| $ \begin{array}{c c} 1 & \bigcirc & 16 \\ 2 & \bigcirc & 15 \\ \end{array} $                 | 3, 4                   | TX Lane 2 (P, N) |

| $\begin{array}{c c} 3 & \bigcirc & 14 \\ 4 & \bigcirc & 13 \\ \hline & & & & \\ \end{array}$ | 5, 6                   | TX Lane 3 (P, N) |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                       | 16, 15                 | TX Lane 4 (P, N) |

|                                                                                              | 12, 11                 | Clock Lane (P,N) |

|                                                                                              | 7, 8, 9, 10, 13 and 14 | NC               |

#### TABLE 3: UPPER MXP CONNECTOR, LANE PINOUT

| CONNECTOR                                                                                    | PIN                | LANE                   |

|----------------------------------------------------------------------------------------------|--------------------|------------------------|

|                                                                                              | 7                  | TX Lane 1 (P, replica) |

| $\begin{array}{c c} 2 & \bigcirc & 13 \\ 3 & \bigcirc & 14 \\ 4 & \bigcirc & 13 \end{array}$ | 8                  | TX Lane 2 (N, replica) |

| $ \begin{array}{c c} 5 & \bigcirc & 12 \\ 6 & \bigcirc & 11 \\ \end{array} $                 | 10                 | TX Lane 4 (P, replica) |

| $ \begin{array}{c} 7 \\ 8 \\ \hline 9 \end{array} $                                          | 1 to 6, 9, 11 - 16 | NC                     |

The 12 pin connector on the left side of the module, as shown in Figure 1, provides access to six GPIO pins and a ground pin. The connector pinout is given in Table 4, and the Molex connector part number is shown in the same table. All GPIO pins are 2.5 V LVCMOS compatible.

Please see the "General Purpose I/O and I2C Bus" section later in this document for the description of the GPIO and pin functions.

| CONNECTOR                   | PIN | INPUT/OUTPUT | INTERNAL<br>PULLUP/<br>PULLDOWN<br>RESISTORS | FUNCTION                              |

|-----------------------------|-----|--------------|----------------------------------------------|---------------------------------------|

|                             | 1   | Configurable | Weak Pull Up                                 | GPIO[0] or<br>Daisy Chain Trigger Out |

| 12 pin GPIO connector       | 2   | Configurable | Weak Pull Up                                 | GPIO[1] or I2C_SCL                    |

| Molex 15-91-2125            | 3   | Configurable | Weak Pull Up                                 | GPIO[2] or I2C_SDA                    |

| 00000000000<br>Pin 12 Pin 1 | 4   | Configurable | Pull Down                                    | GPIO[3]                               |

|                             | 5   | Configurable | Pull Down                                    | GPIO[4]                               |

|                             | 6   | Input Only   | Pull Down                                    | Tearing Effect Input                  |

|                             | 12  | -            | -                                            | Ground                                |

#### TABLE 4: GPIO CONNECTOR PINOUT

#### DATA RATE PERFORMANCE

The SV3C-DPTX data rate may be programmed over a continuous range from 80 Mbps to 6.5 Gbps. The SV3C-DPTX maintains calibrated clock/data alignment and programmed skews are applied over the entire data rate range.

### INTEGRATED LP AND HS GENERATION

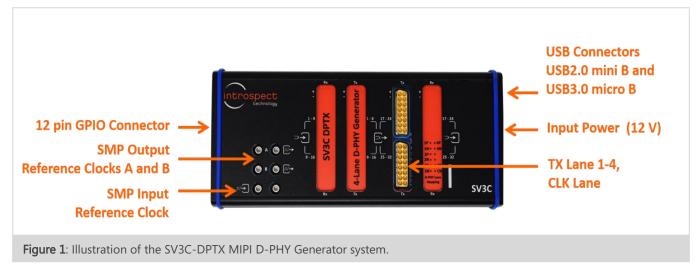

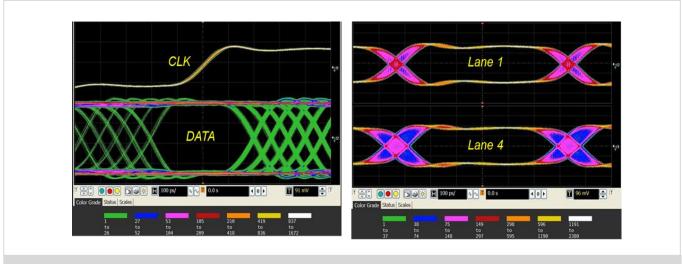

The SV3C-DPTX offers truly integrated LP pattern generation as illustrated in Figure 2(a) and (b). The inclusion of LP allows for the creation of realistic stimulus conditions, and it enables the validation of key MIPI D-PHY global timing parameters. Figure 2(b) illustrates an example of the voltage control of the SV3C-DPTX. Lane 1 in the figure has been programmed with a positive HS common voltage, while Lane 4 has been programmed with a negative common mode voltage.

**Figure 2:** The left-hand figure shows the SV3C-DPTX waveform showing complete packet transmissions. The right-hand figure shows an example of voltage control.

#### **HS TIMING CONTROLS**

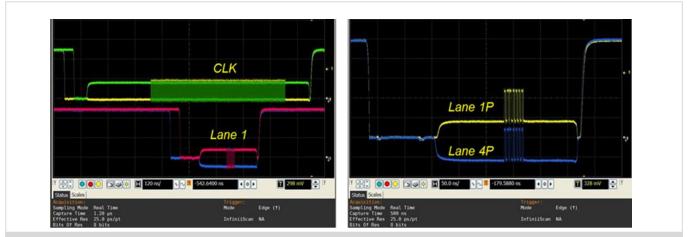

The SV3C-DPTX offers precise control over HS timing with skew adjustment resolution of 1 ps. Figure 3(a) illustrates a sample skew sweep which can be injected between HS clock and the data lines, and Figure 3(b) demonstrates the individual jitter injection control for each HS clock and data lane. In the figure, Lane 4 is programmed to inject higher jitter than Lane 1.

**Figure 3:** SV3C-DPTX generated waveforms demonstrating HS timing control. The left-hand figure shows an example of sweeping skew between CLK and DATA. The right-hand figure is an example of jitter injection.

## COMPLETE PHYSICAL LAYER TESTING

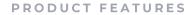

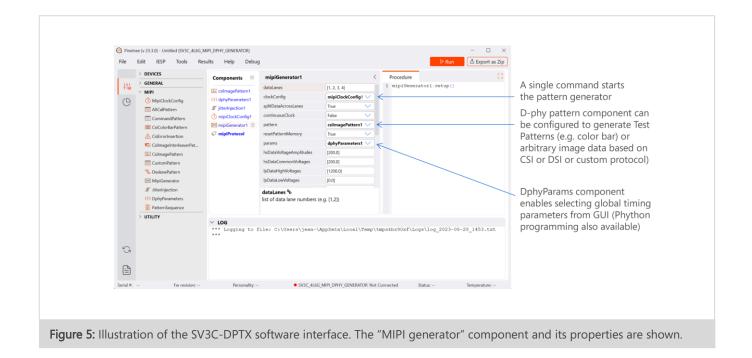

For physical layer testing, the SV3C-DPTX generates highly configurable MIPI D-PHY stimulus signals and provides full control over key timing parameters associated with HS-entry and HS-exit transitions. A list of several key timing parameters controlled by the SV3C-DPTX is given in Table 5 on the following page. Typical waveforms are shown in Figure 4.

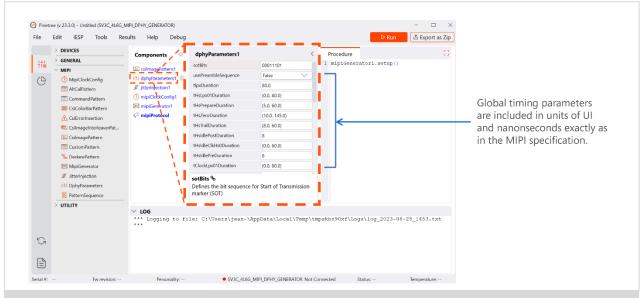

Please also refer to Figure 7 on page 11 for an example of the Pinetree software which shows the intuitive user interface for programming timing parameters.

| PARAMETER TYPE |                                                      | TIMING PARAMETERS                                                                              | PATTERN DEFINITONS                             |

|----------------|------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------------------------|

|                | Clock                                                | T <sub>CLK-LPX</sub> , T <sub>CLK-PREPARE</sub> , T <sub>CLK-ZERO</sub> , T <sub>CLK-PRE</sub> | Start of Transmission (SoT)<br>Clock zero bits |

| HS Entry       | Data                                                 | T <sub>lpx</sub> , T <sub>hs-prepare</sub> , T <sub>hs-zero</sub>                              | Start of Transmission (SoT)<br>HS zero bits    |

| HS Exit        | Clock T <sub>CLK-TRAIL</sub> , T <sub>CLK-POST</sub> |                                                                                                | Clock trail bits                               |

|                | Data                                                 | T <sub>hs-trail</sub> , T <sub>hs-exit</sub>                                                   | HS trail bits                                  |

#### TABLE 5: KEY MIPI TIMING PARAMETER AND BIT PATTERN CONTROLS

Figure 4: Waveforms showing key timing parameter controls available with the SV3C-DPTX.

#### **PROTOCOL LAYER TESTING**

For protocol testing, the Introspect software environment includes MIPI pattern tools that enable the generation of complete DSI-2 or CSI-2 packets, color bars and test patterns. All common pixel formats are supported. The SV3C-DPTX supports DSI-2 features such as the MIPI Display Command Set (DCS) as well as data compression formats (DSC and V-DCM). For further information on supported features refer to Table 12 in the "Specifications" section of this document.

#### **PINETREE INTERFACE**

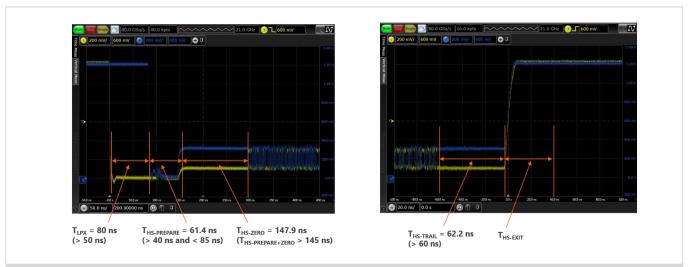

The SV3C-DPTX is operated using award-winning Pinetree software. It features a comprehensive scripting language (Python) and an intuitive component-based design as shown in the screen shots in Figure 5 to Figure 7. Component-based design is Pinetree's way of flexibly organizing the instrument in a manner that allows for easy program development. It highlights to the user only the parameters that are needed for any given task, allowing program development and execution in a matter of minutes.

#### **PRODUCT FEATURES**

| ile        | Edit IESP Tools Re       | esults Help Debug              |                            | ,                        | ⊳ Run                     | ① Export as Zip | imageFiles property selects a list of image files from the |

|------------|--------------------------|--------------------------------|----------------------------|--------------------------|---------------------------|-----------------|------------------------------------------------------------|

|            | GENERAL                  | Components                     | csilmagePattern1           | <                        | Procedure                 | 0               | .\Params folder from which                                 |

| ¦±I<br>†I⊕ | Y MIPI                   | 🖾 csilmagePattern1 💼           | timeUnits                  | nanosecond 🗸             | 1 mipiGeneratorl.setup()  |                 | 🖊 to generate a pattern                                    |

| Θ          | MipiClockConfig          | +++ dphyParameters1            | imageFiles                 | [IntrospectLogo.p 🗸 🧲    |                           |                 |                                                            |

| G          | AltCalPattern            | J jitterInjection1             | imageFormat                | CSI_RGB888 V             |                           |                 | 20 common pixel formats                                    |

|            | CommandPattern           | O mipiClockConfig1             | gaussianBlurRadius         | 0                        |                           |                 |                                                            |

|            | CsiColorBarPattern       | igi mipiGenerator1             | lineTimeMode               | lineTimeTotal 🗸 🗸        |                           |                 | are automatically supported                                |

|            | ↑ CsiErrorInsertion      | 🖉 mipiProtocol                 | horizLineTime              | 30000.0                  |                           |                 | A 11 G                                                     |

|            | 🖾 CsilmageInterleaverPat |                                | frameBlankingMode          | frameRate 🗸              | <b>K</b>                  |                 | <ul> <li>All frame parameters are</li> </ul>               |

|            | SilmagePattern           |                                | frameRate                  | 30.0                     |                           |                 | fully configurable, regardless                             |

|            | CustomPattern            |                                | lineNumbering              | disabled 🗸               |                           |                 | of test pattern                                            |

|            | TeskewPattern            |                                | wantFrameNumbering         | False 🗸                  |                           |                 |                                                            |

|            | MipiGenerator            |                                | enableCsiEpd               | False V                  |                           |                 |                                                            |

|            |                          |                                | timeUnits %                |                          |                           |                 |                                                            |

|            | +++ DphyParameters       |                                | Select the time units to u | use for this component   |                           |                 |                                                            |

|            | PatternSequence          |                                |                            | transmission period of a |                           |                 |                                                            |

|            |                          |                                |                            |                          |                           |                 |                                                            |

|            |                          | LOG<br>*** Logging to f<br>*** | file: C:\Users\jean-\      | AppData\Local\Temp\tm    | skbz90xf\Logs\log_2023-08 | -28_1453.txt    |                                                            |

| G          |                          |                                |                            |                          |                           |                 |                                                            |

| Ē          |                          |                                |                            |                          |                           |                 |                                                            |

Figure 6: Illustration of the SV3C-DPTX software interface. The MIPI "CSI Image Pattern" component and properties are shown.

Figure 7: Illustration of the SV3C-DPTX software interface. The "DPHY Parameters" component and properties are shown.

## MIPI COMPLIANCE TEST SUITES (CTS)

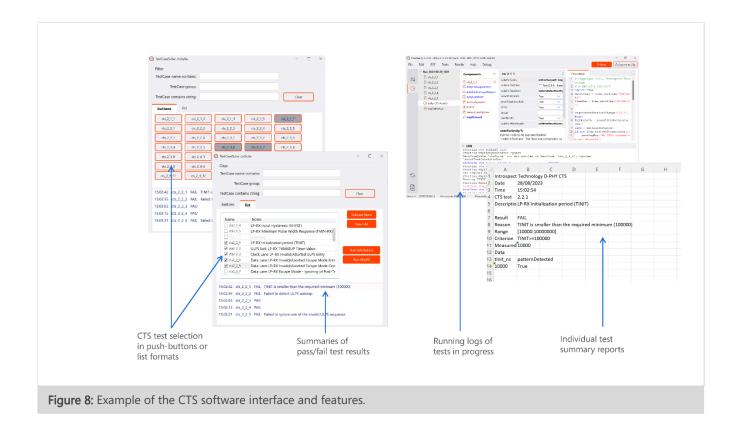

Introspect has implemented MIPI Compliance Test Suites within the Pinetree software environment. This includes test suites for both C-PHY and D-PHY, and for both transmitter and receiver compliance testing. A full list of CTS applications available for the SV3C-DPTX are provided in Table 6 below. An overview of the software interface and features of the D-PHY Receiver CTS Application, as implemented with the SV3C-DPTX MIPI D-PHY Generator, is shown in Figure 8.

Compliance test suites from Introspect provide convenient methods for selecting and executing tests, generate easy-to-read summaries of Pass/Fail compliance test results, and present clear individual summary reports for each compliance test executed. Each CTS application contains code which may be customized, particularly to allow for test automation. For example, custom code can facilitate the execution of external scripts using .NET DLLs to directly control devices under test (DUTs).

| PART<br>NUMBER | DESCRIPTION                          | MIPI SPECIFICATION DOCUMENT         |

|----------------|--------------------------------------|-------------------------------------|

| 5401           | D-PHY Receiver CTS Application       | mipi_D-PHY-v2-1_CTS_v1-0            |

| 5403           | D-PHY CSI-2 Receiver CTS Application | mipi_CSI-2_v1-3_CTS_Receiver_v1-0   |

| 5405           | D-PHY CSI-2 Receiver CTS Application | mipi_CSI-2_v2-1_CTS_Receiver_v1-0   |

| 5404           | D-PHY DSI Receiver CTS Application   | mipi_DSI-v1-3-1_CTS-Receiver_v1-0 * |

#### TABLE 6: MIPI CTS SUITES AVAILABLE FOR THE SV3C-DPTX

\* At the time of publication of this datasheet, mipi\_DSI-v1-3-1\_CTS-Receiver\_v1-0 was the most recent official CTS release approved by MIPI. The DSI-2 CTS will be supported by Introspect once the DSI-2 CTS receives official MIPI board approval.

## INPUT AND OUTPUT REFERENCE CLOCKS

The SV3C-DPTX allows for direct synchronization with an external input reference clock. The input reference frequency range is from 10 MHz to 250 MHz and the reference clock interface is compatible with 1.8 V to 3.3 V LVDS or LVPECL. The SV3C-DPTX also provides two external reference clocks. The output frequency range is from 10 MHz to 500 MHz.

Please see Table for a full listing of input and output reference clock characteristics.

## GENERAL PURPOSE I/O (GPIO) AND I2C BUS

The SV3C-DPTX provides a set of general purpose I/O (GPIO) signals that can be used for either implementing custom test vectors or for programming specialized, pre-defined functions. The pinout for the GPIO was provided in Table 4 previously. Each of the pins listed in Table 4 may be used in one of two ways:

- As configurable GPIO pins, either as inputs or outputs for "Flag" or "Trigger" functions respectively, or

- As pre-defined GPIO pins with functions including:

- "DAISY\_CHAIN\_TRIG\_OUT" (pin 1) which can be used to synchronize the MIPI D-PHY signal outputs of two SV3C-DPTX devices, for increased lane counts

- "I2C\_SCL" and "I2C\_SDA" (pins 2 and 3) which implement an I2C master controller for communicating with DUT devices, and

- "Tearing Effect Input" (pin 6) for DUT testing which includes the MIPI D-PHY tearing effect.

All I/O pins are 2.5 V LVCMOS compatible, and input voltages to these pins should not exceed 2.5 V. Full specifications are given in Table .

Please contact Introspect for coded examples for getting started with GPIO pin functions.

# Specifications

#### TABLE 7: GENERAL SPECIFICATIONS

| PARAMETER                                      | VALUE              | UNITS | DESCRIPTION AND<br>CONDITIONS                        |

|------------------------------------------------|--------------------|-------|------------------------------------------------------|

| Application / Protocol Support                 |                    |       |                                                      |

| Physical layer interface                       | D-PHY              |       |                                                      |

| MIPI protocol                                  | CSI, DSI           |       | CSI-2 v1.3, CSI-2 v2.0, DSI-2 v1.1                   |

| LP/HS Handling                                 | Automatic          |       | Tester automatically generates LP and HS data        |

| Ports                                          |                    |       |                                                      |

| Number of D-PHY Lanes                          | 4 Lanes<br>and CLK |       |                                                      |

| Number of Dedicated Output<br>Reference Clocks | 2                  |       | Individually synthesized frequency and output format |

| Number of Dedicated Input<br>Reference Clocks  | 1                  |       | Used as optional external reference clock input      |

| Number of GPIO pins                            | 6                  |       | Via Molex connector                                  |

| Number of I2C Masters                          | 1                  |       | Via Molex connector, uses GPIO pins                  |

| Connections to PC for Pinetree<br>Control      | 2                  |       | USB2 and USB3                                        |

| HS Output Coupling                             |                    |       |                                                      |

| Output Differential Impedance                  | 100                | Ohm   | For HS operation                                     |

| Differential Impedance Tolerance               | +/- 10             | Ohm   |                                                      |

| Output Single-Ended Impedance                  | 50                 | Ohm   | For HS operation                                     |

| Single-Ended Impedance Tolerance               | +/- 5              | Ohm   |                                                      |

#### TABLE 8: DATA RATES AND TIMING

| PARAMETER                                       | VALUE      | UNITS    | DESCRIPTION AND<br>CONDITIONS                                                                                                                                 |

|-------------------------------------------------|------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HS Timing Performance                           |            |          |                                                                                                                                                               |

| Minimum HS Data Rate                            | 80         | Mbps     |                                                                                                                                                               |

| Maximum HS Data Rate                            | 6.5        | Gbps     |                                                                                                                                                               |

| Frequency Resolution of HS Data<br>Rate         | 1.0        | kbps     |                                                                                                                                                               |

| Rise and Fall Time                              | < 90       | ps       | Typical, 20% to 80%, 1.0 Gbps,<br>400 mVpp differential amplitude,<br>no preEmphasis applied,<br>50 ohm termination to ground                                 |

| Typical Eye Opening<br>Horizontal:<br>Vertical: | 250<br>320 | ps<br>mV | <ul> <li>3.5 Gbps, PRBS9 pattern,</li> <li>400 mVpp differential amplitude,</li> <li>no preEmphasis applied,</li> <li>50 ohm termination to ground</li> </ul> |

| Typical Eye Opening<br>Horizontal:<br>Vertical: | 120<br>200 | ps<br>mV | 6.5 Gbps, PRBS9 pattern,<br>400 mVpp differential amplitude,<br>no preEmphasis applied<br>50 ohm termination to ground                                        |

| LP Timing Performance                           |            |          |                                                                                                                                                               |

| Minimum LP State Period                         | 25         | ns       | LP period is an integer multiple of<br>HS period                                                                                                              |

| Maximum LP State Period                         | 240        | ns       | LP period is an integer multiple of<br>HS period                                                                                                              |

#### TABLE 9: MIPI TRANSMITTER VOLTAGE CHARACTERISTICS

| PARAMETER                                   | VALUE       | UNITS | DESCRIPTION AND<br>CONDITIONS                                       |

|---------------------------------------------|-------------|-------|---------------------------------------------------------------------|

| HS Voltage Performance                      |             |       |                                                                     |

| Minimum Output Voltage Swing                | 20          | mV    | Differential                                                        |

| Maximum Output Voltage Swing                | 600         | mV    | Differential                                                        |

| Voltage Swing Resolution                    | 10          | mV    | Differential                                                        |

| Voltage Swing Accuracy                      | 5% or 15 mV | %, mV | Larger of the percent or mV value                                   |

| Minimum Common Mode Voltage                 | -100        | mV    |                                                                     |

| Maximum Common Mode Voltage                 | 500         | mV    |                                                                     |

| Common Mode Voltage Resolution              | 1.0         | mV    |                                                                     |

| Common Mode Voltage Accuracy                | 8% or 25 mV | %, mV | Larger of the percent or mV value,<br>0 to 500 mV programmed values |

| LP Voltage Controls                         |             |       |                                                                     |

| Minimum Programmable LP Logic<br>High Level | 400         | mV    |                                                                     |

| Maximum Programmable LP Logic<br>High Level | 1200        | mV    |                                                                     |

| Minimum Programmable LP Logic<br>Low Level  | -100        | mV    |                                                                     |

| Maximum Programmable LP Logic               | 600         | mV    |                                                                     |

| Low Level                                   |             |       |                                                                     |

| Logic Level Control Resolution              | 1.0         | mV    |                                                                     |

| Logic Level Accuracy                        | 5% or 20 mV | %, mV | Larger of the percent or mV value                                   |

#### TABLE 10: MIPI TRANSMITTER CHARACTERISTICS

| PARAMETER                                                 | VALUE        | UNITS  | DESCRIPTION AND<br>CONDITIONS             |

|-----------------------------------------------------------|--------------|--------|-------------------------------------------|

| Lane Skew Performance                                     |              |        |                                           |

| Coarse Skew Range:                                        |              |        |                                           |

| Minimum Programmable Skew,<br>in Integer UI               | -20          | UI     | Lane to Lane                              |

| Coarse Skew Range:                                        |              |        |                                           |

| Maximum Programmable Skew,<br>in Integer UI               | +20          | UI     | Lane to Lane                              |

| Fine Skew Range:                                          |              |        |                                           |

| Minimum Programmable Skew                                 | -500         | ps     | Clock to Data                             |

| Fine Skew Range:                                          |              |        |                                           |

| Maximum Programmable Skew                                 | +500         | ps     | Clock to Data                             |

| Fine Skew Injection Resolution                            | 1.0          | ps     |                                           |

| Data to Clock Calibrated Offset                           | 0.5 UI       | UI     | Default factory calibrated data to        |

|                                                           | +/- 0.15 UI  |        | clock offset, valid across all data rates |

| Jitter and Noise Performance                              |              |        |                                           |

| Maximum RJ (random Jitter) noise                          | 3.5          |        | Measured differentially, clock or data    |

| floor                                                     | 5.5          | ps RMS | Data Rate from 1.0 Gbps to 6.5 Gbps       |

| DJ (deterministic jitter) injection,<br>minimum Frequency | 0.1          | kHz    | Sinusoidal jitter                         |

| DJ injection, maximum frequency                           | 50           | MHz    | Sinusoidal jitter                         |

| DJ injection, frequency resolution                        | 0.1          | kHz    |                                           |

| DJ injection, maximum magnitude                           | 2            | UI pp  | 1 MHz frequency jitter                    |

|                                                           |              |        | Tested to a maximum of 1000 ps            |

| DJ injection, magnitude resolution                        | 500          | fs     |                                           |

| DJ injection, accuracy                                    | 10% or 10 ps | %, ps  | Larger of the percent or ps value         |

#### TABLE 11: PATTERN MEMORY AND SEQUENCING

| PARAMETER                                          | VALUE | UNITS  | DESCRIPTION AND<br>CONDITIONS                                                                                |

|----------------------------------------------------|-------|--------|--------------------------------------------------------------------------------------------------------------|

| User-Programmable Pattern Memory                   |       |        |                                                                                                              |

| Minimum Pattern Segment Size                       | 8     | Bits   |                                                                                                              |

| Maximum Pattern Segment Size                       | 4     | GBytes | For additional memory,<br>contact Introspect                                                                 |

| Total Memory Space for Transmitters                | 4     | GBytes | For additional memory, contact Introspect                                                                    |

| Pattern Sequencer                                  |       |        |                                                                                                              |

| Sequence Control                                   | Yes   |        | Loop infinite<br>Loop-on-count (see count below)<br>Play to end                                              |

| Number of Sequencer Slots per<br>Pattern Generator | 16    |        | Each pattern generator can string up<br>to 16 different segments together,<br>each with its own repeat count |

| Number of Entry Slots                              | 1     |        | Separate from above 16 segments                                                                              |

| Number of Exit Slots                               | 1     |        | Separate from above 16 segments                                                                              |

| Maximum Repeat Count Per Slot                      | 65536 |        |                                                                                                              |

| Maximum Repeat Count for Outer<br>Loop             | 65536 |        | Outer loop can encompass any number of slots                                                                 |

| Additional Pattern Characteristics                 |       |        |                                                                                                              |

| Escape Mode Command Entry                          | Yes   |        | Per lane                                                                                                     |

| Pattern Switching                                  | Yes   |        | Wait to end of segment, or immediate                                                                         |

#### TABLE 12: DATA FORMATS AND MIPI PROTOCOL FEATURES

| PARAMETER                     | VALUE               | UNITS | DESCRIPTION AND CONDITIONS                                                                                                    |

|-------------------------------|---------------------|-------|-------------------------------------------------------------------------------------------------------------------------------|

| Supported Pixel Formats       |                     |       |                                                                                                                               |

| Supported Pixel Formats (CSI) | RAW,<br>RGB,<br>YUV |       | RAW6, RAW7, RAW8, RAW10, RAW12,<br>RAW14, RAW16, RAW20, RGB444, RGB555,<br>RGB565, RGB666, RGB888, YUV420, YUV422             |

| Supported Pixel Formats (DSI) | RGB<br>YCbCr        |       | RGB101010, RGB121212, RGB332, RGB565,<br>RGB666, RGB888, YCbCr420_12bit,<br>YCbCr422_16bit, YCbCr422_20bit,<br>YCbCr422_24bit |

| Supported Features            |                     |       |                                                                                                                               |

| ALP support (CSI)             | Yes                 |       |                                                                                                                               |

| EDP support (CSI)             | Yes                 |       |                                                                                                                               |

| Display Command Set (DSI)     | Yes                 |       |                                                                                                                               |

| Data Compression (DSI)        | Yes                 |       | DSC, V-DCM                                                                                                                    |

| Data Scrambling (DSI)         | Yes                 |       | Data payload and footer                                                                                                       |

| Tearing Effect (DSI)          | Yes                 |       |                                                                                                                               |

| Bus-Turn Around               | Yes                 |       | CSI and DSI                                                                                                                   |

| Virtual Channel Support       | Yes                 |       | CSI and DSI                                                                                                                   |

| Packet Error Insertion        | Yes                 |       | CSI and DSI                                                                                                                   |

#### TABLE 13: ENVIRONMENTAL CONDITIONS

| PARAMETER         | VALUE    | UNITS   | DESCRIPTION AND<br>CONDITIONS |

|-------------------|----------|---------|-------------------------------|

| Features          |          |         |                               |

| Temperature Range | 10 to 25 | Celsius | Ambient temperature           |

| Humidity Range    | 35 to 55 | %       |                               |

#### TABLE 14: REFERENCE CLOCK CHARACTERISTICS

| PARAMETER                                        | VALUE | UNITS | DESCRIPTION AND<br>CONDITIONS                                    |

|--------------------------------------------------|-------|-------|------------------------------------------------------------------|

| Reference Clocks                                 |       |       |                                                                  |

| Minimum External Input Clock<br>Frequency        | 10    | MHz   |                                                                  |

| Maximum External Input Clock<br>Frequency        | 250   | MHz   |                                                                  |

| Frequency Resolution of<br>Programmed Data Rate  | 1     | kHz   |                                                                  |

| Supported External Input Clock I/O<br>Standards  |       |       | LVDS (typical 400 mVpp input)<br>LVPECL (typical 800 mVpp input) |

| Minimum Output Clock Frequency                   | 10    | MHz   |                                                                  |

| Maximum Output Clock Frequency                   | 500   | MHz   |                                                                  |

| Output Clock Frequency Resolution                | 1     | kHz   |                                                                  |

| Supported External Output Clock<br>I/O Standards |       |       | LVDS, LVPECL, CML, HCSL, and<br>LVCMOS                           |

#### TABLE 15: GPIO AND I2C BUS VOLTAGE CHARACTERISTICS

| PARAMETER               | VALUE | UNITS | DESCRIPTION AND<br>CONDITIONS     |

|-------------------------|-------|-------|-----------------------------------|

| Voltage                 |       |       |                                   |

| Voltage Level           | 2.5   | V     | All GPIOs operate at 2.5 V LVCMOS |

| V <sub>IL</sub> minimum | -0.3  | V     |                                   |

| V <sub>IL</sub> maximum | 0.7   | V     |                                   |

| V <sub>IH</sub> minimum | 1.7   | V     |                                   |

| V <sub>IH</sub> maximum | 2.5   | V     |                                   |

| V <sub>OL</sub> maximum | 0.4   | V     |                                   |

| V <sub>OH</sub> minimum | 2.0   | V     |                                   |

#### TABLE 16: PHYSICAL CHARACTERISTICS

| PARAMETER                | VALUE     | UNITS  | DESCRIPTION AND<br>CONDITIONS      |

|--------------------------|-----------|--------|------------------------------------|

| Dimensions               |           |        |                                    |

| Length                   | 9.5, 242  | in, mm |                                    |

| Width                    | 4.25, 108 | in, mm |                                    |

| Height                   | 1.3, 34   | in, mm |                                    |

| Weight                   | 2         | lbs    |                                    |

| Physical Connections     |           |        |                                    |

| Lane 1 to Lane 4, Clock  | MXP       |        | Huber & Suhner, 16 pin             |

| GPIO                     |           |        | Available through 12 pin header    |

|                          |           |        | Molex 15-91-2125                   |

| Ref Clock In             | SMP       |        | SMP Differential Pair              |

| Ref Clock Out            | SMP       |        | SMP Differential Pair              |

| PC connection            | USB2      |        | USB2.0 mini B                      |

|                          | USB3      |        | USB3.0 micro B                     |

| Power Switch / Connector |           |        | AC adapter provided                |

|                          |           |        | 110/220 V, 50/60 Hz                |

| Power Consumption        |           |        |                                    |

| DC Input Voltage         | 12        | Volt   |                                    |

| Current Draw             | 4.2       | Amp    | 6.5 Gbps / 4 Lane, HS-only pattern |

| Current Draw             | 3.6       | Amp    | 3.5 Gbps / 4 Lane, HS-only pattern |

| REVISION NUMBER | HISTORY                                                                                                             | DATE               |

|-----------------|---------------------------------------------------------------------------------------------------------------------|--------------------|

| 1.0             | Document creation                                                                                                   | July 26, 2014      |

| 1.1             | Updated document template                                                                                           | June 4, 2015       |

| 1.2             | Updated voltage specifications                                                                                      | January 29, 2016   |

| 1.3             | Updated data rate                                                                                                   | April 20, 2018     |

|                 | specifications, adding ordering information                                                                         |                    |

| 1.4             | Updated Figure 5 and Table 3;<br>added Table 6                                                                      | June 20, 2018      |

| 1.5             | Updated document template,<br>updated voltage and timing<br>specifications, general feature<br>description updates. | June 7, 2021       |

| 1.6             | Updated document template,<br>updated voltage and timing<br>specifications.                                         | July 5, 2021       |

| 1.7             | Updated all screenshots and software mentions to Pinetree                                                           | August 31, 2023    |

| 1.8             | Added a table for<br>Environmental Conditions<br>(Table 13); Updated Logic Level<br>Accuracy in Table 9             | September 19, 2024 |

The information in this document is subject to change without notice and should not be construed as a commitment by Introspect Technology. While reasonable precautions have been taken, Introspect Technology assumes no responsibility for any errors that may appear in this document.

© Introspect Technology, 2024 Published in Canada on September 19, 2024 MK-D013E-E-24263

INTROSPECT.CA